# EE 330 Lecture 31

# Basic amplifier architectures

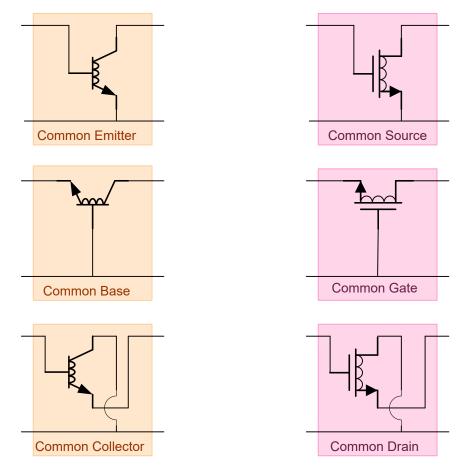

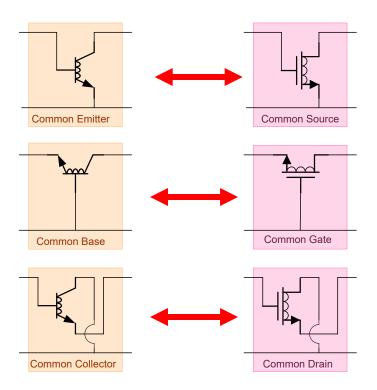

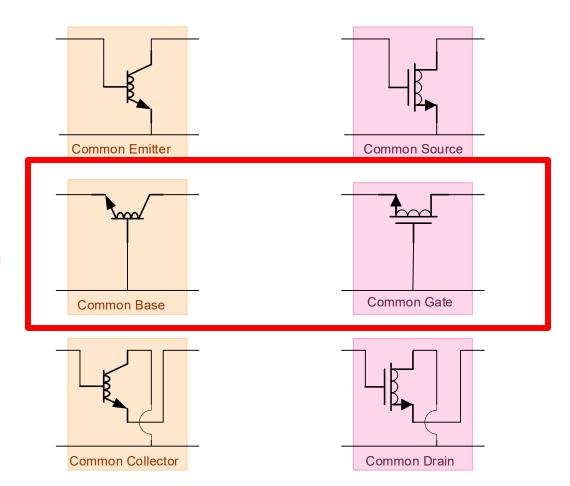

- Common Emitter/Source

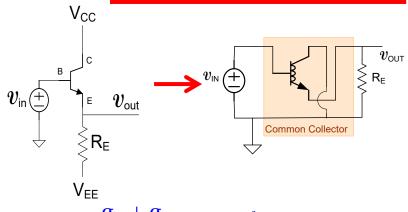

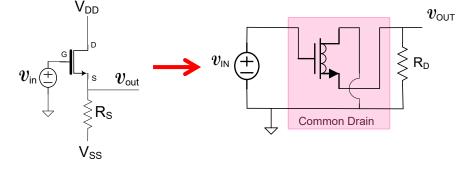

- Common Collector/Drain

- Common Base/Gate

# Spring 2024 Exam Schedule

Exam 1 Friday Feb 16

Exam 2 Friday March 8

Exam 3 Friday April 19

Final Exam Tuesday May 7 7:30 AM - 9:30 AM

#### Review from Last Lecture

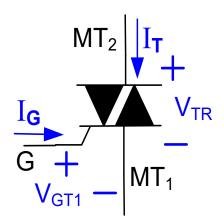

The ideal Triac

# $I_G=0$ $-V_{BGF}$ $I_G=I_{G1}<0$ or $-V_{BGF}$

The Triac

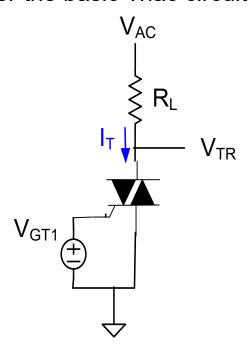

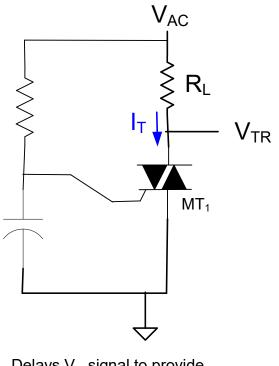

Consider the basic Triac circuit

#### Review from Last Lecture

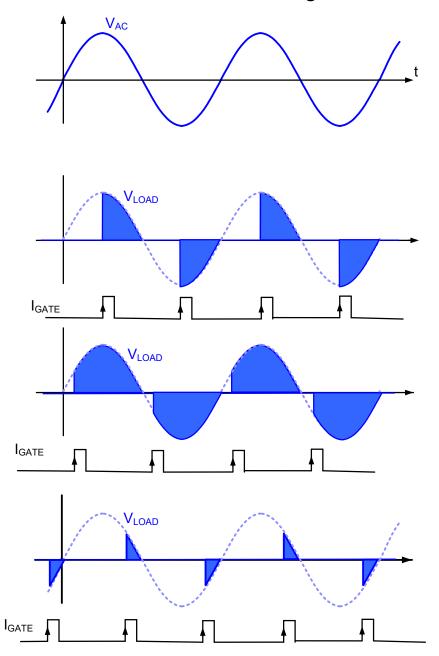

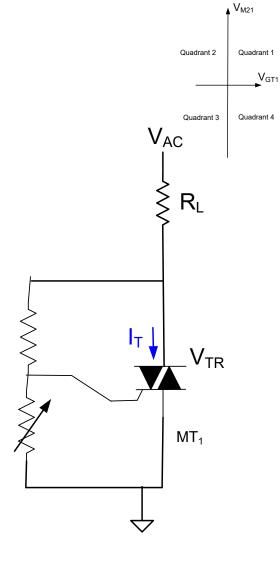

Phase controlled bidirectional switching with Triacs

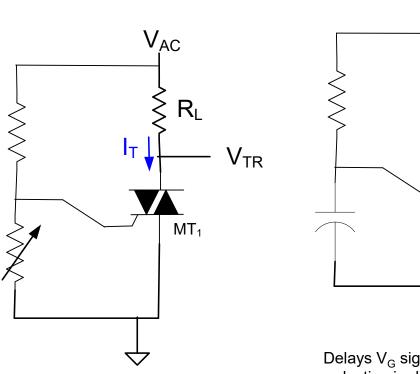

#### Some Basic Triac Application Circuits

Delays V<sub>G</sub> signal to provide reduction in duty cycle

Quad 1: Quad 3

Quad 1: Quad 3

Quad 1: Quad 3

# The Thyristor

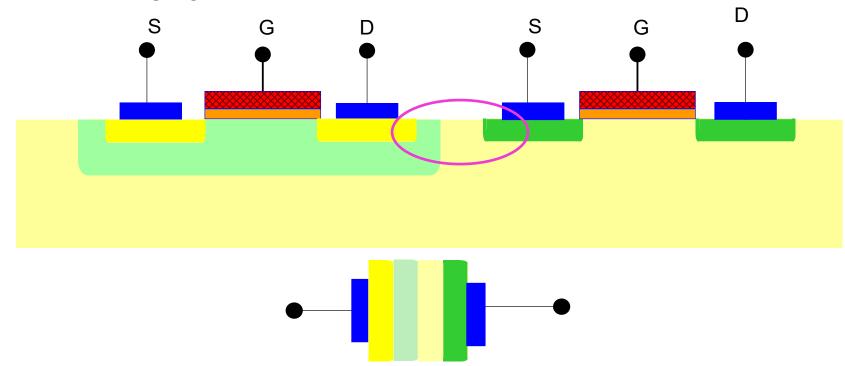

A bipolar device in CMOS Processes

Consider a Bulk-CMOS Process

If this parasitic SCR turns on, either circuit will latch up or destroy itself Guard rings must be included to prevent latchup

Design rules generally include provisions for guard rings

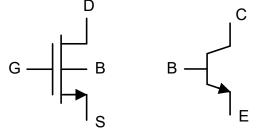

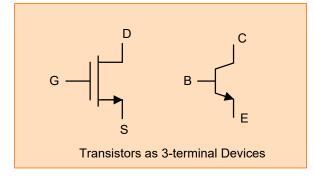

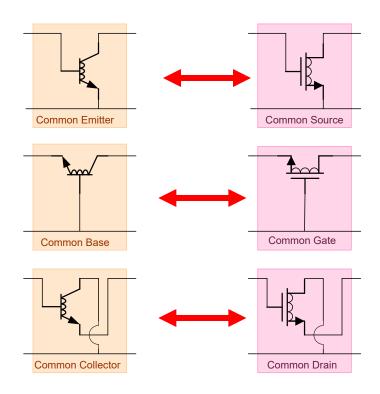

• MOS and Bipolar Transistors both have 3 primary terminals

• MOS transistor has a fourth terminal that is generally considered a parasitic

terminal

#### Observation:

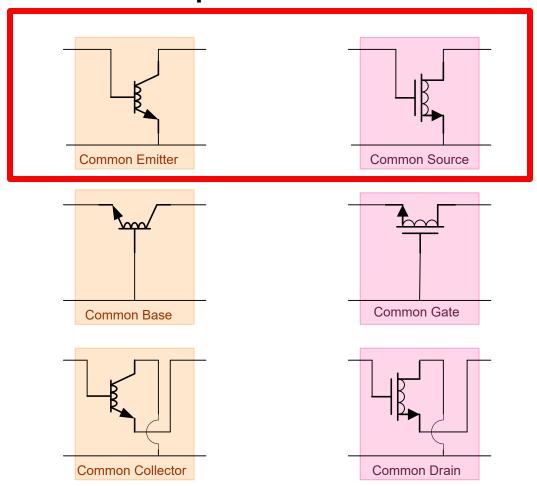

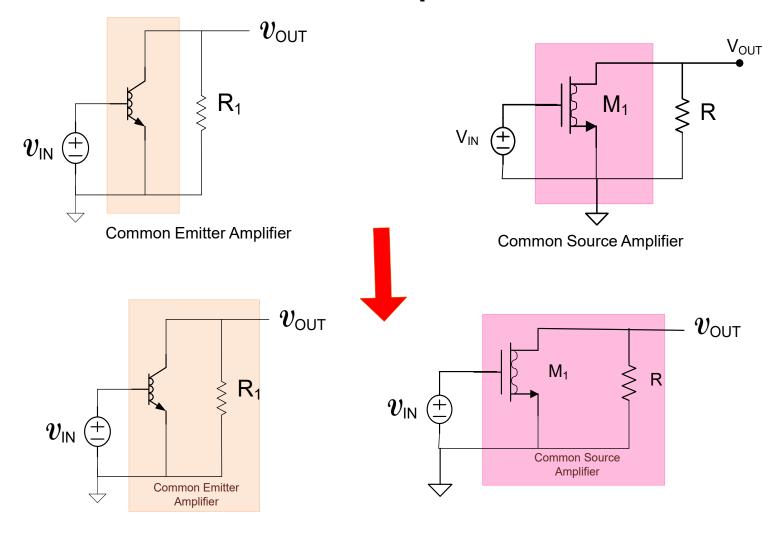

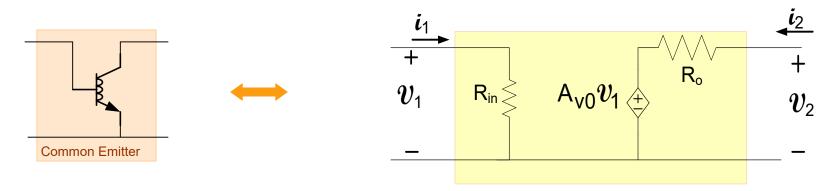

These circuits considered previously have a terminal (emitter or source) common to the input and output ports in the small-signal equivalent circuit

For BJT, E is common, input on B, output on C

Termed "Common Emitter"

For MOSFET, S is common, input on G, output on D

Termed "Common Source"

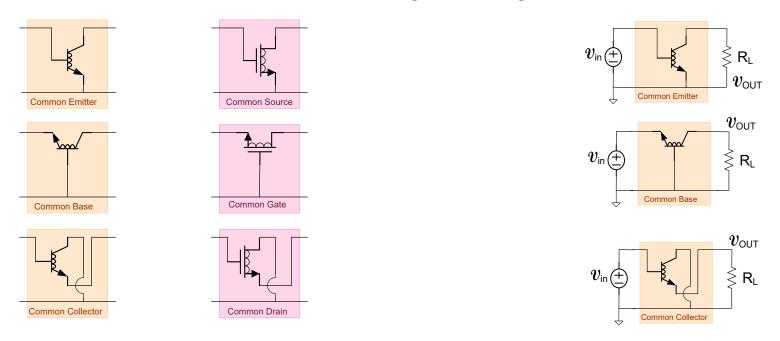

Amplifiers using these devices generally have one terminal common and use remaining terminals as input and output

Since devices are nearly unilateral, designation of input and output terminals is uniquely determined

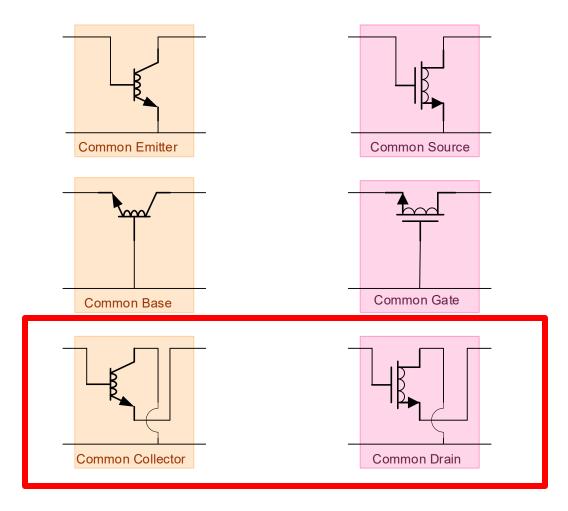

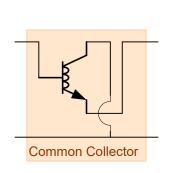

Three different ways to designate the common terminal

Source or Emitter termed Common Source or Common Emitter

Gate or Base termed Common Gate or Common Base

Drain or Collector termed Common Drain or Common Collector

**Common Source or Common Emitter**

**Common Gate or Common Base**

**Common Drain or Common Collector**

| MOS    |       |        |  |  |

|--------|-------|--------|--|--|

| Common | Input | Output |  |  |

| S      | G     | D      |  |  |

| G      | S     | D      |  |  |

| D      | G     | S      |  |  |

| ВЈТ   |                 |  |  |  |

|-------|-----------------|--|--|--|

| Input | Output          |  |  |  |

| В     | С               |  |  |  |

| Е     | С               |  |  |  |

| В     | Е               |  |  |  |

|       | Input<br>B<br>E |  |  |  |

Identification of Input and Output Terminals is not arbitrary

It will be shown that all 3 of the basic amplifiers are useful!

**Common Source or Common Emitter**

**Common Gate or Common Base**

**Common Drain or Common Collector**

#### Objectives in Study of Basic Amplifier Structures

- 1. Obtain key properties of each basic amplifier

- 2. Develop method of designing amplifiers with specific characteristics using basic amplifier structures

# Characterization of Basic Amplifier Structures

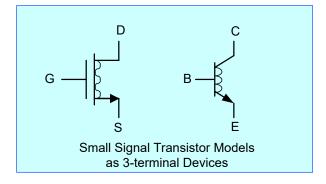

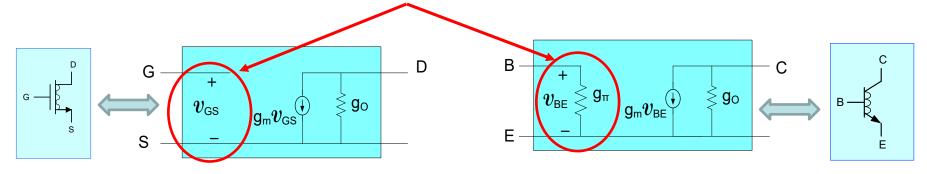

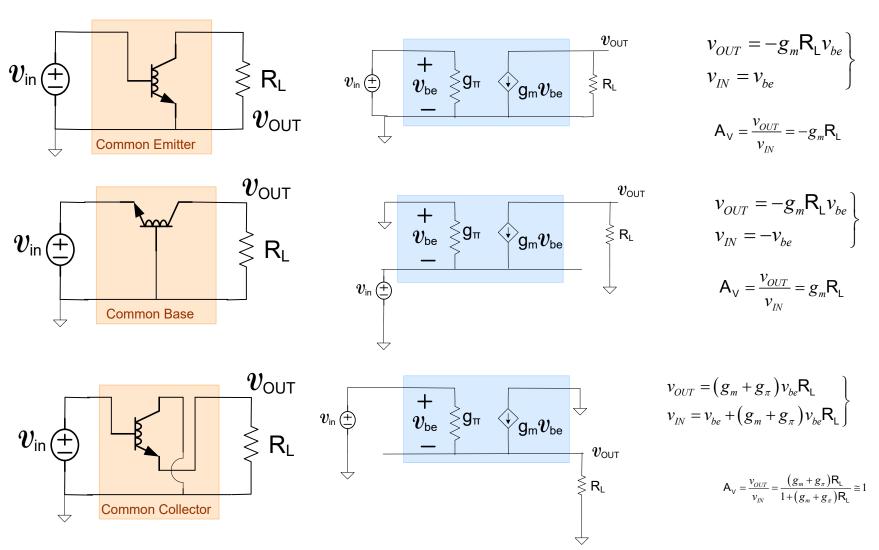

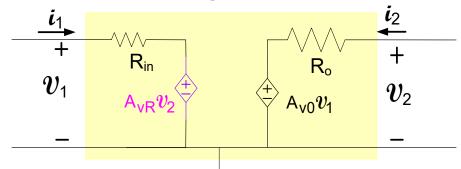

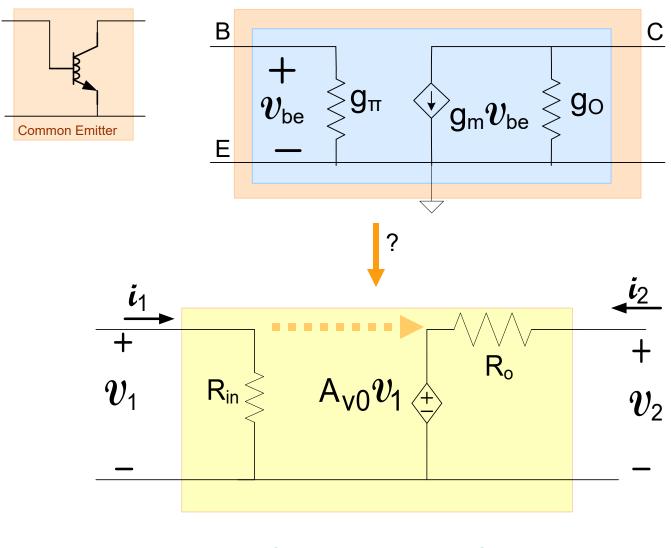

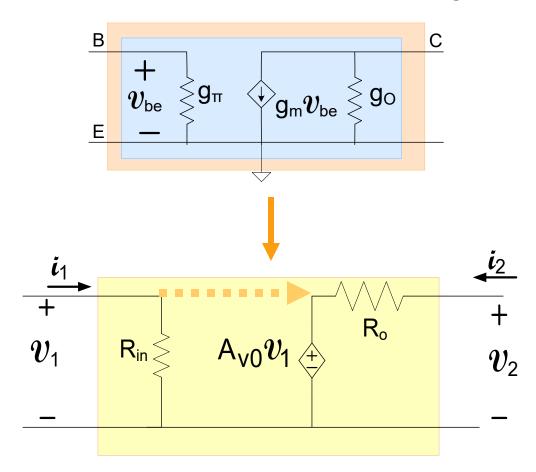

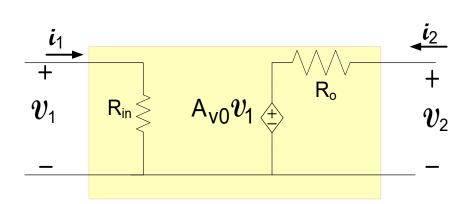

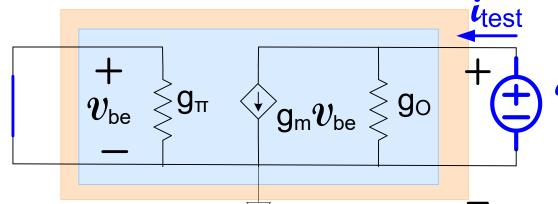

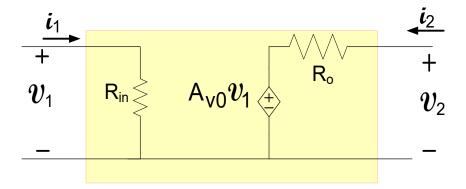

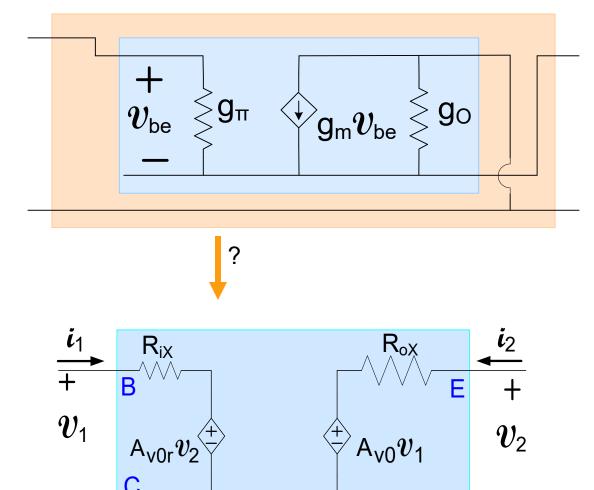

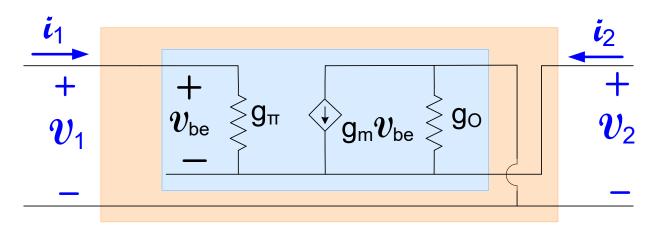

- Observe that the small-signal equivalent of any 3-terminal network is a two-port

- Thus to characterize any of the 3 basic amplifier structures, it suffices to determine the two-port equivalent network

- Since small signal model when expressed in terms of small-signal parameters of BJT and MOSFET differ only in the presence/absence of  $g_{\pi}$  term, can analyze the BJT structures and then obtain characteristics of corresponding MOS structure by setting  $g_{\pi}$ =0

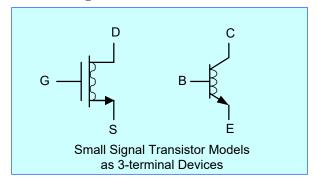

# The three basic amplifier types for both MOS and bipolar processes

Will focus on the performance of the bipolar structures and then obtain performance of the MOS structures by observation

# The three basic amplifier types for both MOS and bipolar processes

- Significantly different gain characteristics for the three basic amplifiers

- There are other significant differences too (R<sub>IN</sub>, R<sub>OUT</sub>, ...) as well

# The three basic amplifier types for both MOS and bipolar processes

More general models are needed to accommodate biasing, understand performance capabilities, and include effects of loading of the basic structures

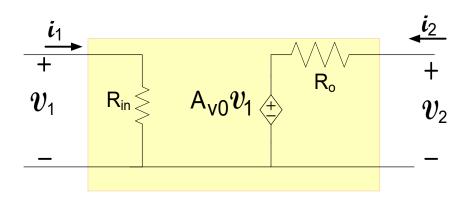

Two-port models are useful for characterizing the basic amplifier structures

How can the two-port parameters be obtained for these or any other linear two-port networks?

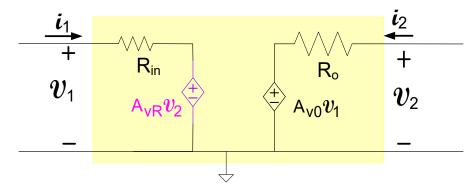

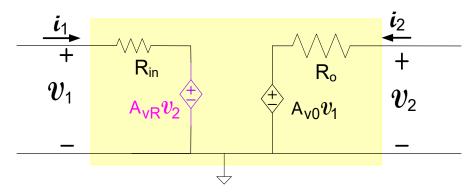

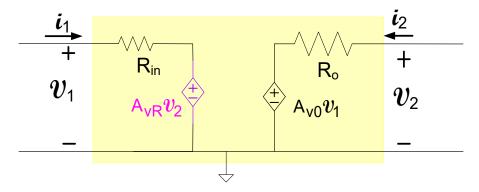

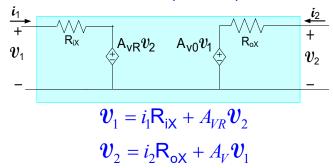

# Two-Port Models of Basic Amplifiers widely used for Analysis and Design of Amplifier Circuits

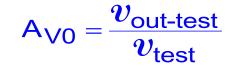

# Methods of Obtaining Amplifier Two-Port Network

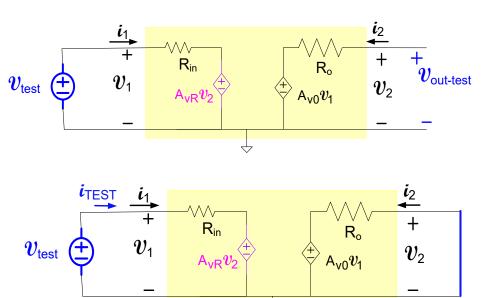

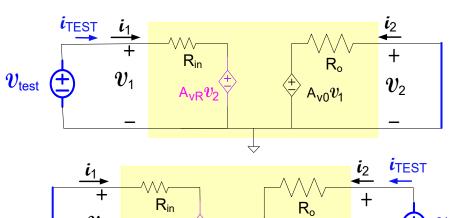

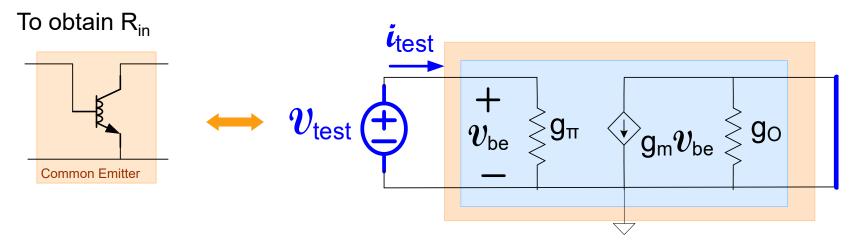

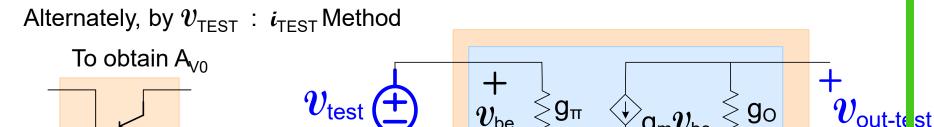

- 1.  $v_{\mathsf{TEST}}$  :  $i_{\mathsf{TEST}}$  Method (considered in a previous lecture)

- 2. Write  $v_1$ :  $v_2$  equations in standard form

$$v_1 = i_1 R_{IN} + A_{VR} v_2$$

$$v_2 = i_2 R_O + A_{VO} v_1$$

- 3. Thevenin-Norton Transformations

- 4. Ad Hoc Approaches

Any of these methods can be used to obtain the two-port model

# If Unilateral A <sub>VR</sub> =0

## $v_{ m test}$ : $i_{ m test}$ Method for Obtaining Two-Port Amplifier Parameters **SUMMARY from PREVIOUS LECTURE**

$$R_{in} = \frac{v_{test}}{i_{test}}$$

$$\mathsf{R}_0 = rac{oldsymbol{v}_{\mathsf{test}}}{oldsymbol{\iota}_{\mathsf{test}}}$$

$$v_{\text{out-test}}$$

$v_{\text{1}}$   $v_{\text{2}}$   $v_{\text{2}}$   $v_{\text{2}}$   $v_{\text{2}}$   $v_{\text{2}}$

$$\mathsf{A}_\mathsf{VR} = rac{v_\mathsf{out\text{-}test}}{v_\mathsf{test}}$$

Will now develop two-port model for each of the three basic amplifiers and look at one widely used application of each

#### Parameter Domains for Small-Signal Models for Any Devices

Small-signal parameter domain

Y-parameters, g-parameters, amplifier parameters, ...

- Model Parameters and Operating Point (MPOP)

- Small-signal analysis naturally results in small-signal parameter domain

- More insight often in MPOP domain

- Mixed-parameter domains possible but often difficult to obtain insight

#### Parameter Domains for Small-Signal Models for Any Devices

Small-signal parameter domain

Y-parameters, g-parameters, amplifier parameters, ...

Model Parameters and Operating Point (MPOP)

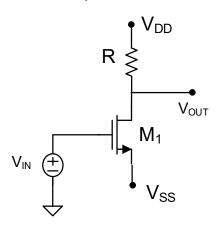

Example: Give A<sub>V</sub> for basic amplifier in ss parameter domain and MPOP domain

Small-Signal parameter domain

$$A_{V} = \frac{v_{OUT}}{v_{N}} = -g_{m}R$$

MPOP domain

$$A_{V} = \frac{v_{OUT}}{v_{IN}} = -2\frac{I_{DQ}R}{V_{FB}}$$

# Consider Common Emitter/Common Source Two-port Models

- Will focus on Bipolar Circuit since MOS counterpart is a special case obtained by setting  $g_{\pi}$ =0

- Will consider both two-port model and a widely used application

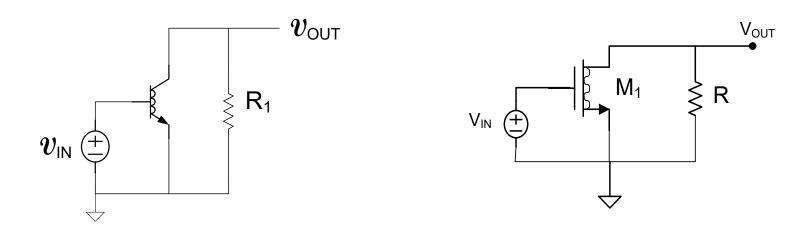

# Basic CE/CS Amplifier Structures

Can include or exclude R and R<sub>1</sub> in two-port models (of course they are different circuits)

The CE and CS amplifiers are themselves two-ports!

$\{R_i, A_{V0} \text{ and } R_0\}$

# Two-Port Models of Basic Amplifiers widely used for Analysis and Design of Amplifier Circuits

## Methods of Obtaining Amplifier Two-Port Network

- 1.  $v_{\mathsf{TEST}}$  :  $i_{\mathsf{TEST}}$  Method

- 2. Write  $v_1 : v_2$  equations in standard form  $v_1 = i_1 R_{IN} + A_{VR} v_2$  $v_2 = i_2 R_O + A_{VO} v_1$

- 3. Thevenin-Norton Transformations

- 4. Ad Hoc Approaches

By Thevenin: Norton Transformations

$$R_{in} = \frac{1}{g_{\pi}}$$

$$A_{V0} = -\frac{g_m}{g_0}$$

$$R_0 = \frac{1}{g_0}$$

$$A_{VR} = 0$$

# Two-Port Models of Basic Amplifiers widely used for Analysis and Design of Amplifier Circuits

## Methods of Obtaining Amplifier Two-Port Network

- 1.  $v_{\mathsf{TEST}}$  :  $i_{\mathsf{TEST}}$  method

- 2. Write  $v_1 : v_2$  equations in standard form  $v_1 = i_1 R_{IN} + A_{VR} v_2$  $v_2 = i_2 R_O + A_{VO} v_1$

- 3. Thevenin-Norton Transformations

- 4. Ad Hoc Approaches

Alternately, by  $v_{\mathsf{TEST}}$  :  $\emph{i}_{\mathsf{TEST}}$  Method

$$\mathsf{R}_\mathsf{in} = rac{oldsymbol{v}_\mathsf{test}}{oldsymbol{\iota}_\mathsf{test}}$$

$$R_{in} = \frac{1}{g_{\pi}}$$

$\{R_{in}, A_{V0} \text{ and } R_0\}$

$$\mathsf{A}_{\mathsf{V0}} = rac{v_{\mathsf{out est}}}{v_{\mathsf{test}}}$$

$$\mathbf{v}_{out-test} = \mathbf{v}_{test} \left( -\frac{\mathbf{g}_m}{\mathbf{g}_0} \right)$$

$$A_{V0} = -\frac{g_m}{g_0}$$

$\{R_{in}, A_{V0} \text{ and } R_0\}$

**Common Emitter**

$$R_0 = \frac{v_{\text{test}}}{i_{\text{test}}}$$

$$\mathbf{v}_{test} = i_{test}(\mathbf{g}_0)$$

$$R_0 = \frac{1}{g_0}$$

$\{R_{in}, A_{V0} \text{ and } R_0\}$

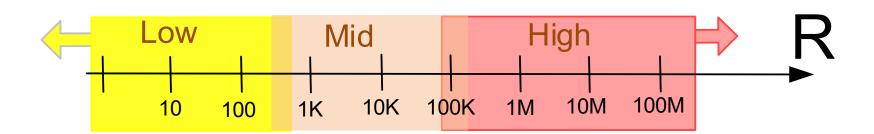

# Impedance Range and Classification

The terms "High Impedance" and "Low Impedance" are often used

Whether an impedance is considered high or low or mid-range is a relative assessment

When building MOS or BJT amplifiers, the following relative notation of impedance levels is often useful (though there may be some extreme applications where even this notation is not standard)

# Impedance Range and Classification

Ideal Port Impedance of the four basic amplifiers

| Amplifier Type   | R <sub>IN</sub> | R <sub>OUT</sub> |

|------------------|-----------------|------------------|

| Voltage          | 8               | 0                |

| Current          | 0               | 8                |

| Transconductance | 8               | <b>∞</b>         |

| Transresistance  | 0               | 0                |

In terms of small signal model parameters:

$$R_{in} = \frac{1}{g_{\pi}}$$

$A_{V0} = -\frac{g_m}{g_0}$   $R_0 = \frac{1}{g_0}$   $A_{VR} = 0$

In terms of operating point and model parameters:

$$R_i = \frac{\beta V_t}{I_{CQ}} \qquad A_{V0} = -\frac{V_{AF}}{V_t} \qquad R_0 = \frac{V_{AF}}{I_{CQ}} \qquad \qquad A_{VR} = 0$$

#### **Characteristics:**

- Input impedance is mid-range

- Voltage Gain is Large and Inverting

- Output impedance is large

- Unilateral

- Widely used to build voltage amplifiers

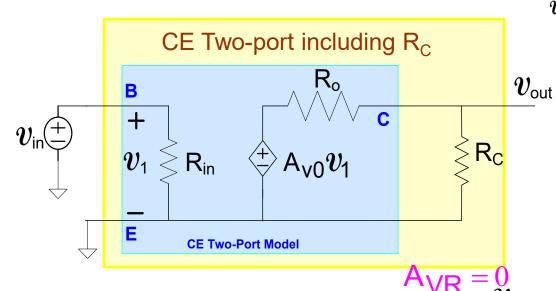

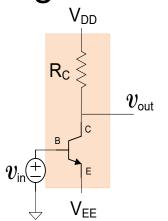

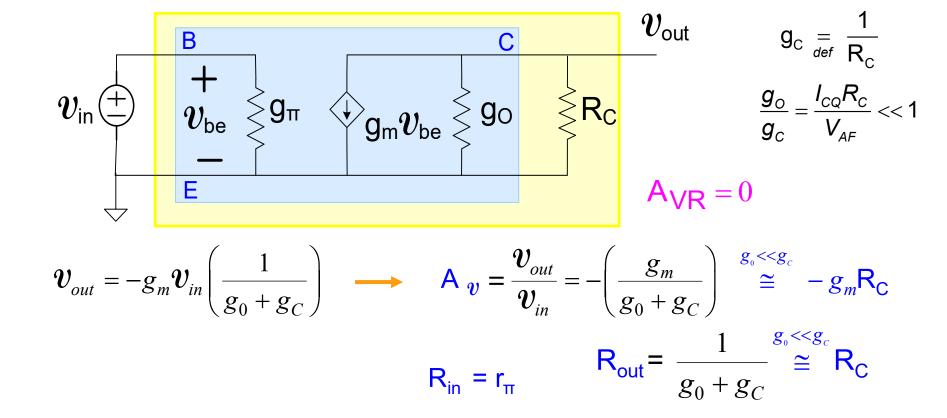

# **Common Emitter Configuration**

#### Consider the following CE application

(this will also generate a two-port model for this CE application)

$$g_C = \frac{1}{R_C}$$

$$\frac{g_{\rm O}}{g_{\rm C}} = \frac{I_{\rm CQ}R_{\rm C}}{V_{\rm AF}} << 1$$

$$\boldsymbol{v}_{out}(g_C + g_0) = g_0 A_{V0} \boldsymbol{v}_{in} \longrightarrow A_{VC} = \frac{\boldsymbol{v}_{out}}{\boldsymbol{v}_{in}} = \frac{g_0 A_{V0}}{g_0 + g_C} = \frac{-g_m}{g_0 + g_C} \stackrel{g_0 << g_c}{\cong} -g_m R_C$$

$$R_{inC} = R_{in} = r_{\pi}$$

$$R_{outC} = R_o //R_C \longrightarrow R_{outC} = R_o //R_C = \frac{1}{g_0 + g_C} \stackrel{g_0 \sim g_c}{\cong} R_c$$

## Common Emitter Configuration

#### Consider the following CE application

(this will also generate a two-port model for this CE application)

This circuit can also be analyzed directly without using 2-port model for CE configuration (use standard 2-port transistor model instead)

# Common Emitter Configuration

#### Consider the following CE application

(this is also a two-port model for this CE application)

Small-signal parameter domain

Operating point and model parameter domain

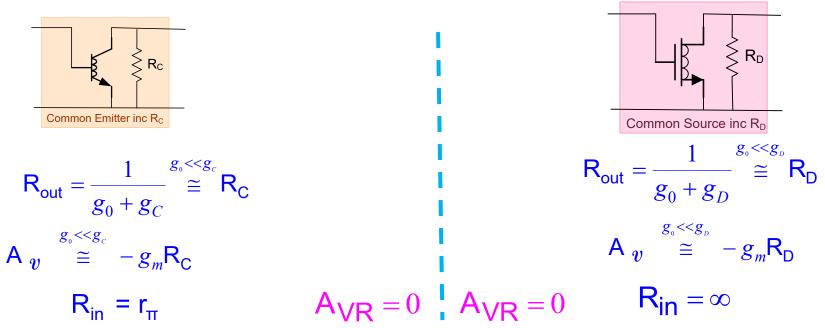

$$A_{v} \stackrel{g_{o} << g_{c}}{\cong} -g_{m}R_{C}$$

$$R_{out} = \frac{1}{g_{0} + g_{C}} \stackrel{g_{o} << g_{c}}{\cong} R_{C}$$

$$R_{in} = r_{\pi}$$

$$A_{VR} = 0$$

$$A_{v} \stackrel{g_{0} << g_{c}}{\cong} -\frac{I_{CQ}R_{C}}{V_{t}}$$

$$R_{out} \stackrel{g_{0} << g_{c}}{\cong} R_{C}$$

$$R_{in} = \frac{\beta V_t}{I_{CQ}}$$

#### **Characteristics:**

- Input impedance is mid-range

- Voltage Gain is large and Inverting

- Output impedance is mid-range

- Unilateral

- Widely used as a voltage amplifier

# Common Source/ Common Emitter Configurations

$$R_{in} = \frac{1}{g_{\pi}}$$

$$A_{V0} = -\frac{g_m}{g_0}$$

$$R_{in} = \frac{1}{g_{\pi}} \qquad A_{V0} = -\frac{g_m}{g_0} \qquad R_0 = \frac{1}{g_0} \qquad R_{in} = \infty \qquad A_{V0} = -\frac{g_m}{g_0} \qquad R_0 = \frac{1}{g_0}$$

$$A_{V0} = -\frac{g_m}{g_0}$$

$$R_0 = \frac{1}{g_0}$$

In terms of operating point and model parameters:

$$R_{in} = \frac{\beta V_t}{I_{CQ}}$$

$$A_{V0} = -\frac{V_{AF}}{V_t} \qquad I$$

$$R_0 = \frac{V_{AF}}{I_{CQ}}$$

$$R_{in} = \frac{\beta V_t}{I_{CQ}} \qquad A_{V0} = -\frac{V_{AF}}{V_t} \qquad R_0 = \frac{V_{AF}}{I_{CQ}} \qquad R_0 = \frac{1}{\lambda I_{DQ}} = \frac{V_{AF}}{I_{DQ}} = \frac{V_{AF}}{I_{DQ}} = \frac{V_{AF}}{V_{EBQ}} = -2\frac{V_{AF}}{V_{EBQ}} = -2\frac{V_{AF}}{V_{E$$

#### Characteristics:

- Input impedance is mid-range (infinite for MOS)

- Voltage Gain is Large and Inverting

- Output impedance is large

- Unilateral

- Widely used to build voltage amplifiers

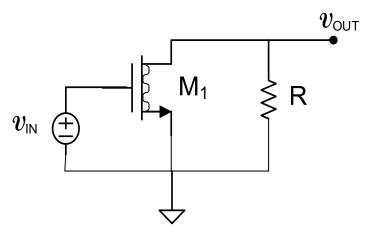

## Common Source/Common Emitter Configuration

Widely used CE application (but also a two-port)

In terms of operating point and model parameters:

- $R_{in} = \frac{\beta V_t}{I_{con}}$  Voltage Gain is Large and Inverting Output impedance is mid-range

- Unilateral

- Widely used as a voltage amplifier

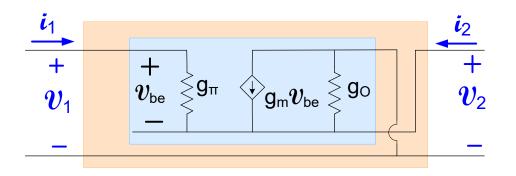

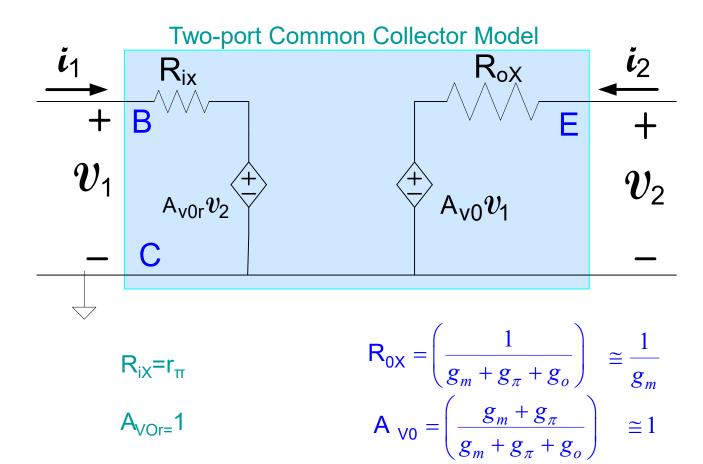

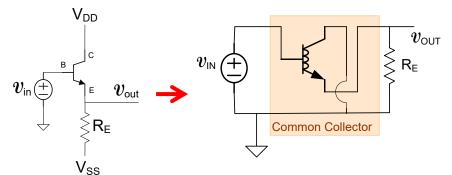

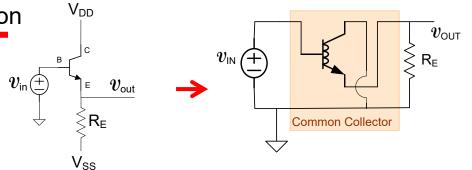

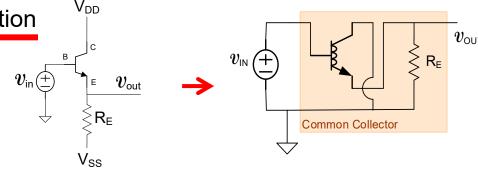

## Consider Common Collector/Common Drain Two-port Models

- Will focus on Bipolar Circuit since MOS counterpart is a special case obtained by setting  $g_{\pi}$ =0

- Will consider both two-port model and a widely used application

$\{R_{iX}, A_{V0}, A_{V0r} \text{ and } R_{0X}\}$

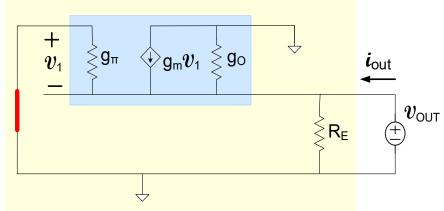

## Two-Port Models of Basic Amplifiers widely used for Analysis and Design of Amplifier Circuits

#### Methods of Obtaining Amplifier Two-Port Network

1.  $v_{\mathsf{TEST}}$  :  $i_{\mathsf{TEST}}$  Method

- Thevenin-Norton Transformations

- 4. Ad Hoc Approaches

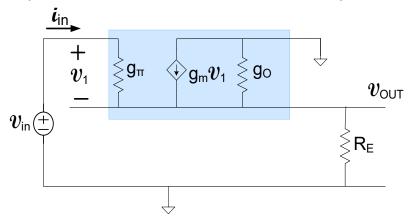

Applying KCL at the input and output node, obtain

$$i_1 = (\mathbf{V}_1 - \mathbf{V}_2) g_{\pi}$$

$$i_2 = (g_m + g_{\pi} + g_o) \mathbf{V}_2 - (g_m + g_{\pi}) \mathbf{V}_1$$

These can be rewritten as

$$\mathbf{v}_{1} = i_{1}\mathbf{r}_{\pi} + \mathbf{v}_{2}$$

$$\mathbf{v}_{2} = \left(\frac{1}{g_{m} + g_{\pi} + g_{o}}\right)\mathbf{i}_{2} + \left(\frac{g_{m} + g_{\pi}}{g_{m} + g_{\pi} + g_{o}}\right)\mathbf{v}_{1}$$

Standard Two-Port Amplifier Representation

$v_1$ :  $v_2$  equations in standard form

It thus follows that

$$R_{iX} = r_{\pi}$$

$A_{VOr} = 1$   $R_{0X} = \left(\frac{1}{g_m + g_{\pi} + g_o}\right)$   $A_{VO} = \left(\frac{g_m + g_{\pi}}{g_m + g_{\pi} + g_o}\right)$

$$A_{V0} = \left(\frac{g_m + g_\pi}{g_m + g_\pi + g_o}\right)$$

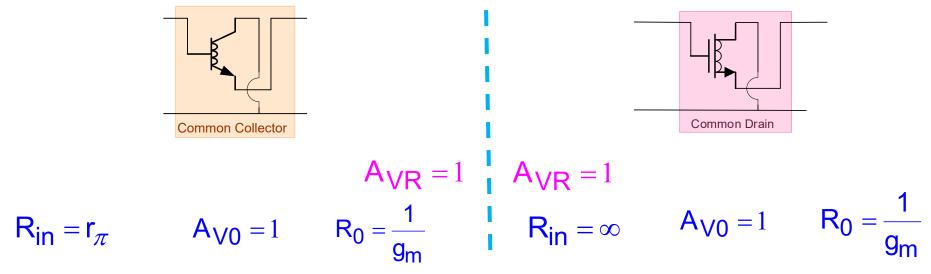

In terms of operating point and model parameters:

$$R_{in} = \frac{\beta V_t}{I_{CQ}} \qquad \qquad A_{V0} = 1 \qquad \qquad R_0 = \frac{V_t}{I_{CQ}} \qquad \qquad R_{in} = \infty \qquad A_{V0} = 1 \qquad R_0 = \frac{V_{EB}}{2I_{DQ}}$$

Characteristics:

- Input impedance is mid-range (infinite for MOS)

- Voltage Gain is nearly 1

- Output impedance is very low

- Slightly non-unilateral (critical though in increasing input impedance when R<sub>F</sub> added)

- Widely used as a buffer

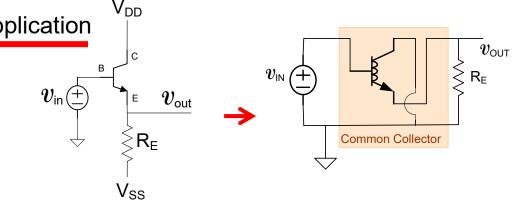

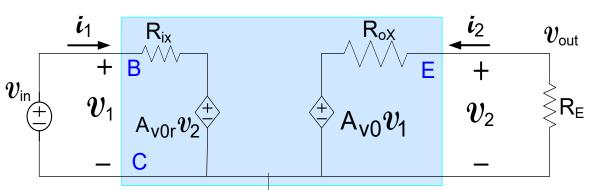

Consider the following popular CC application

#### Determine $R_{in}$ , $R_0$ , and $A_V$

(this is not asking for a two-port model for the CC application;  $R_{\rm in}$  and  $A_{\rm V}$  defined for no additional load on output,  $R_{\rm o}$  defined for short-circuit input)

$$\frac{g_m}{g_{RE}} = \frac{I_{CQ}R_E}{V_t} >> 1$$

$$A_{V} = A_{V0} \frac{g_{ox}}{g_{ox} + g_{RE}} = \frac{g_{m} + g_{\pi}}{g_{m} + g_{\pi} + g_{o}} \left( \frac{g_{m} + g_{\pi} + g_{o}}{g_{m} + g_{\pi} + g_{o} + g_{RE}} \right) = \frac{g_{m} + g_{\pi}}{g_{m} + g_{\pi} + g_{o} + g_{RE}} \cong \frac{g_{m}}{g_{m} + g_{RE}} \stackrel{if g_{m} >> g_{RE}}{\cong} 1$$

$$v_{\text{in}} = i_{1}R_{\text{ix}} + A_{\text{v0r}}A_{\text{v0}} \frac{g_{0X}}{g_{0X} + g_{\text{RE}}} v_{\text{in}} \qquad \Rightarrow R_{\text{in}} = \frac{r_{\pi}}{1 - \frac{g_{m} + g_{\pi}}{g_{m} + g_{\pi} + g_{o} + g_{\text{RE}}}} = r_{\pi} \frac{g_{m} + g_{\pi} + g_{o} + g_{\text{RE}}}{g_{o} + g_{\text{RE}}} \stackrel{g_{\pi E} >> g_{o}}{\cong} r_{\pi} + \beta R_{\text{E}}$$

$$R_0 \cong \frac{1}{g_m + g_{RE} + g_0 + g_{\pi}} = \frac{1}{g_m + g_{RE}} = \frac{R_E}{1 + g_m R_E} \stackrel{g_m >> g_{RE}}{\cong} \frac{1}{g_m}$$

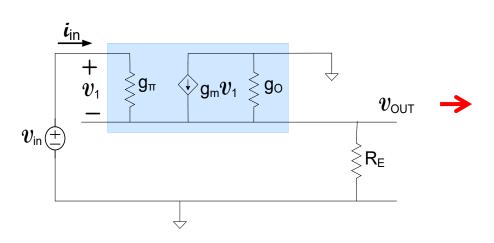

#### Consider the following popular CC application

#### Determine $R_{in}$ , $R_0$ , and $A_V$

(this is not asking for a two-port model for the CC application;  $R_{in}$  and  $A_{V}$  defined for no additional load on output,  $R_{o}$  defined for short-circuit input)

#### Alternately, this circuit can also be analyzed directly

$$\frac{g_m}{g_{RE}} = \frac{I_{CQ}R_E}{V_t} >> 1$$

$$oldsymbol{V}_{out} \left( oldsymbol{g}_{RE} + oldsymbol{g}_0 + oldsymbol{g}_{\pi} + oldsymbol{g}_m oldsymbol{V}_1$$

$oldsymbol{V}_{in} = oldsymbol{V}_1 + oldsymbol{V}_{out}$

$$A_{V} = \frac{g_{\pi} + g_{n} + g_{n} + g_{n} + g_{n}}{g_{m} + g_{RE} + g_{0} + g_{\pi}} = \frac{g_{m}}{g_{m} + g_{RE}} = \frac{I_{CQ}R_{E}}{I_{CQ}R_{E} + V_{t}} \approx 1$$

$$\boldsymbol{i}_{in} = \boldsymbol{g}_{\pi} (\boldsymbol{V}_{in} - \boldsymbol{V}_{out})$$

$$\boldsymbol{V}_{out} (\boldsymbol{g}_{m} + \boldsymbol{g}_{RE} + \boldsymbol{g}_{0} + \boldsymbol{g}_{\pi}) = \boldsymbol{V}_{in} (\boldsymbol{g}_{\pi} + \boldsymbol{g}_{m})$$

$$i_{in}(g_m + g_\pi + g_{RE} + g_0) = g_\pi v_{in}(g_{RE} + g_0)$$

$$R_{in} = r_\pi \frac{g_m + g_\pi + g_o + g_{RE}}{g_o + g_{RE}} \stackrel{\underline{g_{RE}} >> g_o}{\cong} r_\pi + \beta R_E$$

Consider the following popular CC application

Determine  $R_{in}$ ,  $R_0$ , and  $A_V$

(this is not asking for a two-port model for the CC application;  $R_{in}$  and  $A_{V}$  defined for no additional load on output,  $R_{o}$  defined for short-circuit input )

Alternately, this circuit can also be analyzed directly (continued)

To obtain  $R_0$ , set  $V_{in} = 0$

$$\frac{g_m}{g_{RE}} = \frac{I_{CQ}R_E}{V_t} >> 1$$

$$\boldsymbol{i}_{out} = \boldsymbol{V}_{out} (g_{RE} + g_0 + g_\pi) - g_m (-\boldsymbol{V}_{out})$$

$$\mathsf{R}_{\mathsf{out}} = \frac{1}{g_m + g_\pi + g_o + g_{RE}} \stackrel{g_{\scriptscriptstyle E} << g_{\scriptscriptstyle m}}{\cong} \frac{1}{g_m}$$

#### Consider the following popular CC application

(this is not asking for a two-port model for the CC application,  $-R_{in}$  and  $A_{V}$  defined for no additional load on output,  $R_{o}$  defined for short-circuit input -)

$$A_{V} = \frac{g_{\pi} + g_{m}}{g_{m} + g_{RE} + g_{0} + g_{\pi}} \cong \frac{g_{m}}{g_{m} + g_{RE}} = \frac{I_{CQ}R_{E}}{I_{CQ}R_{E} + V_{t}} \cong 1$$

$$R_{in} = r_{\pi} \frac{g_m + g_{\pi} + g_o + g_{RE}}{g_o + g_{RE}} \stackrel{g_{RE} >> g_o}{\cong} r_{\pi} + \beta R_{E}$$

$$\mathsf{R}_{\mathsf{out}} = \frac{1}{g_m + g_\pi + g_o + g_{RE}} \stackrel{g_{\scriptscriptstyle E} << g_o}{\cong} \frac{1}{g_m}$$

Question: Why are these not the two-port parameters of this circuit?

- R<sub>in</sub> defined for open-circuit on output instead of shortcircuit (see previous slide: -2 slides)

- $A_{VOr} \neq 0$

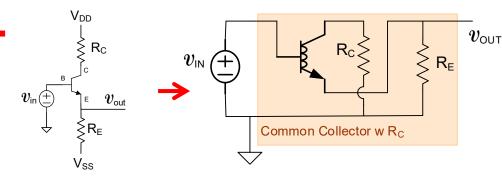

## Common Collector Configuration with R<sub>C</sub>

#### Consider the following CC application

(though not real common, sometimes a resistor is included in the collector)

It can be readily shown that unless  $R_C$  is very large, it has little effect on the performance and have same expressions for  $A_V$ ,  $R_{IN}$ , and  $R_{OUT}$

$$A_{V} \cong \frac{g_{m}}{g_{m} + g_{E}} = \frac{I_{CQ}R_{E}}{I_{CQ}R_{E} + V_{t}} \cong 1$$

$$R_{in} \cong r_{\pi} + \beta R_{E}$$

$$R_{\text{out}} \cong \frac{1}{g_m}$$

Intuitively this can be expected since if  $g_0$  is neglected,  $R_C$  is in series with a current source in the ss BJT model

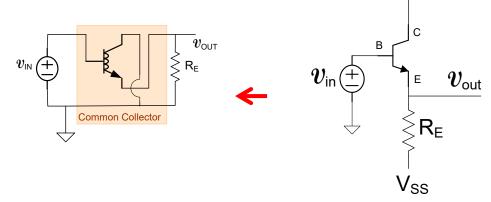

#### For this popular CC application

(this is not a two-port model for this CC application)

$V_{DD}$

#### Small signal parameter domain

$$A_{V} = \frac{g_{\pi} + g_{m}}{g_{m} + g_{RE} + g_{0} + g_{\pi}} \stackrel{if g_{m} >> g_{RE}}{\cong} 1$$

$$R_{in} \stackrel{g_{\scriptscriptstyle E} >> g_{\scriptscriptstyle o}}{\cong} r_{\pi} + \beta R_{E}$$

$$R_0 \cong \frac{R_E}{1 + g_m R_E} \stackrel{g_m R_E >> 1}{\cong} \frac{1}{g_m}$$

Operating point and model parameter domain

$$A_{V} \cong \frac{I_{CQ}R_{E}}{I_{CQ}R_{E} + V_{t}} \stackrel{I_{co}R_{E} >> V_{t}}{\cong} 1$$

$$R_{in} \stackrel{I_{co}R_{E}>>V_{t}}{\cong} r_{\pi} + \beta R_{E}$$

$$R_0 \stackrel{I_{oo}R_{\epsilon}>>V_{t}}{\cong} \frac{V_{t}}{I_{CQ}}$$

#### Characteristics:

- Output impedance is low

- A<sub>V0</sub> is positive and near 1

- Input impedance is very large

- Widely used as a buffer

- Not completely unilateral but output-input transconductance (or A<sub>Vr</sub>) is small and effects are generally negligible though magnitude same as A<sub>V</sub>

## Common Collector/Common Drain Configurations

For these popular CC/CD applications (not two-port models for these applications)

$$A_{V} = \frac{g_{\pi} + g_{m}}{g_{m} + g_{E} + g_{0} + g_{\pi}} \stackrel{if g_{m} >> g_{E}}{\cong} 1$$

$$R_{\text{in}} \stackrel{g_{\scriptscriptstyle E} >> g_{\scriptscriptstyle o}}{\cong} r_{\scriptscriptstyle \Pi} + \beta R_{\scriptscriptstyle E}$$

$$R_0 \cong \frac{R_{\scriptscriptstyle E}}{1 + g_{\scriptscriptstyle m} R_{\scriptscriptstyle E}} \stackrel{g_{\scriptscriptstyle m} R_{\scriptscriptstyle E} >> 1}{\cong} \frac{1}{g_{\scriptscriptstyle m}}$$

$$=\frac{g_{\scriptscriptstyle m}R_{\scriptscriptstyle E}>>1}{\cong}\frac{1}{g_{\scriptscriptstyle m}}$$

$$A_{V} = \frac{g_{m}}{g_{m} + g_{S} + g_{0}} \stackrel{if g_{m} >> g_{s}}{\cong} 1$$

$$R_{in} = \infty$$

$$R_0 \cong \frac{R_S}{1 + g_m R_S} \stackrel{g_m R_S >> 1}{\cong} \frac{1}{g_m}$$

In terms of operating point and model parameters:

$$\begin{aligned} A_{V} &\cong \frac{I_{CQ}R_{E}}{I_{CQ}R_{E} + V_{t}} \overset{I_{co}R_{E} >> V_{t}}{\cong} 1 \qquad R_{0} \overset{I_{co}R_{E} >> V_{t}}{\cong} \frac{V_{t}}{I_{CQ}} \\ R_{in} &\cong r_{\pi} + \beta R_{E} \end{aligned}$$

$$\begin{split} A_{V} &\cong \frac{ \cdot 2 I_{DQ} R_{S}}{2 I_{DQ} R_{S} + V_{EBQ}} \underbrace{ if \ 2 I_{DQ} R_{s} >> V_{EBQ}}_{2 I_{DQ} R_{S} + V_{EBQ}} \underbrace{ \ 1}_{2 I_{DQ} R_{s} >> V_{EBQ}} \underbrace{ V_{EBQ} R_{S}}_{2 I_{DQ} R_{S}} \underbrace{ V_{EBQ} V_{EBQ}}_{2 I_{DQ}} \end{split}$$

$R_{in} = \infty$

- Output impedance is low

- $A_{1/0}$  is positive and near 1

- Input impedance is very large

- Widely used as a buffer

- Not completely unilateral but output-input transconductance is small

# Consider Common Collector/Common Drain Two-port Models

Remains to study the Common Base/Common Gate configuration

- Will focus on Bipolar Circuit since MOS counterpart is a special case obtained by setting  $g_{\pi}$ =0

- Will consider both two-port model and a widely used application

Stay Safe and Stay Healthy!

## **End of Lecture 31**